(2)Verilog HDL Bits:设计电路实现Thermostat(温度调节器)

1.1 目录

(1)目录

(2)FPGA介绍

(3)Verilog HDL Bits:设计电路实现Thermostat(温度调节器)

(4)原理和代码讲解

1.2 FPGA简介

FPGA是在PAL、GAL、EPLD、CPLD等可编程器件的基础上进一步发展的产物。它是作为ASIC领域中的一种半定制电路而出现的,即解决了定制电路的不足,又克服了原有可编程器件门电路有限的缺点。

FPGA采用了逻辑单元阵列LCA(Logic Cell Array)这样一个概念,内部包括可配置逻辑模块CLB(Configurable Logic Block)、输入输出模块IOB(Input Output Block)和内部连线(Interconnect)三个部分。 现场可编程门阵列(FPGA)是可编程器件,与传统逻辑电路和门阵列(如PAL,GAL及CPLD器件)相比,FPGA具有不同的结构。FPGA利用小型查找表(16×1RAM)来实现组合逻辑,每个查找表连接到一个D触发器的输入端,触发器再来驱动其他逻辑电路或驱动I/O,由此构成了既可实现组合逻辑功能又可实现时序逻辑功能的基本逻辑单元模块,这些模块间利用金属连线互相连接或连接到I/O模块。FPGA的逻辑是通过向内部静态存储单元加载编程数据来实现的,存储在存储器单元中的值决定了逻辑单元的逻辑功能以及各模块之间或模块与I/O间的联接方式,并最终决定了FPGA所能实现的功能,FPGA允许无限次的编程。

1.3 Verilog HDL Bits:设计电路实现Thermostat(温度调节器)

本题在HDL Bits题库中的位置为Circuits/Combinational Logic/Basic Gates/Thermostat

题目要求:恒温器有两种模式:加热模式(mode = 1)和冷却模式(mode = 0),在加热模式下,温度过低(too_cold = 1)时打开加热器,但不使用空调。在制冷模式下,当温度过高(too_hot = 1)时,请打开空调,但不要打开暖气。当加热器或空调打开时,也要打开风扇,让空气流通。此外,用户还可以要求打开风扇(fan_on = 1),即使加热器和空调关闭。尝试只使用赋值语句,看看是否可以转换问题描述。

由题可画真值表:

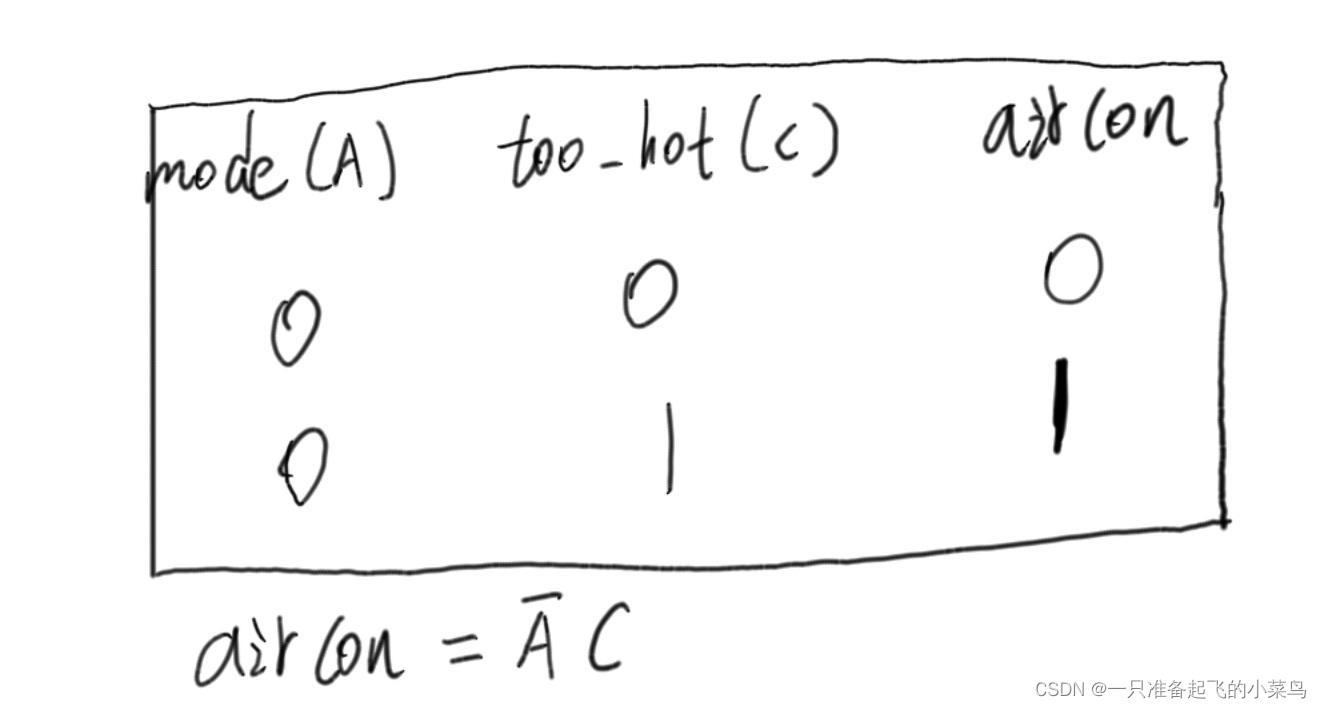

由题可知,空调(aircon)是否打开主要与模式(mode)和过热信号(too_hot)有关,所以对其列真值表得到,空调(aircon)的开关值逻辑表达式。

由题可知,空调(aircon)是否打开主要与模式(mode)和过热信号(too_hot)有关,所以对其列真值表得到,空调(aircon)的开关值逻辑表达式。

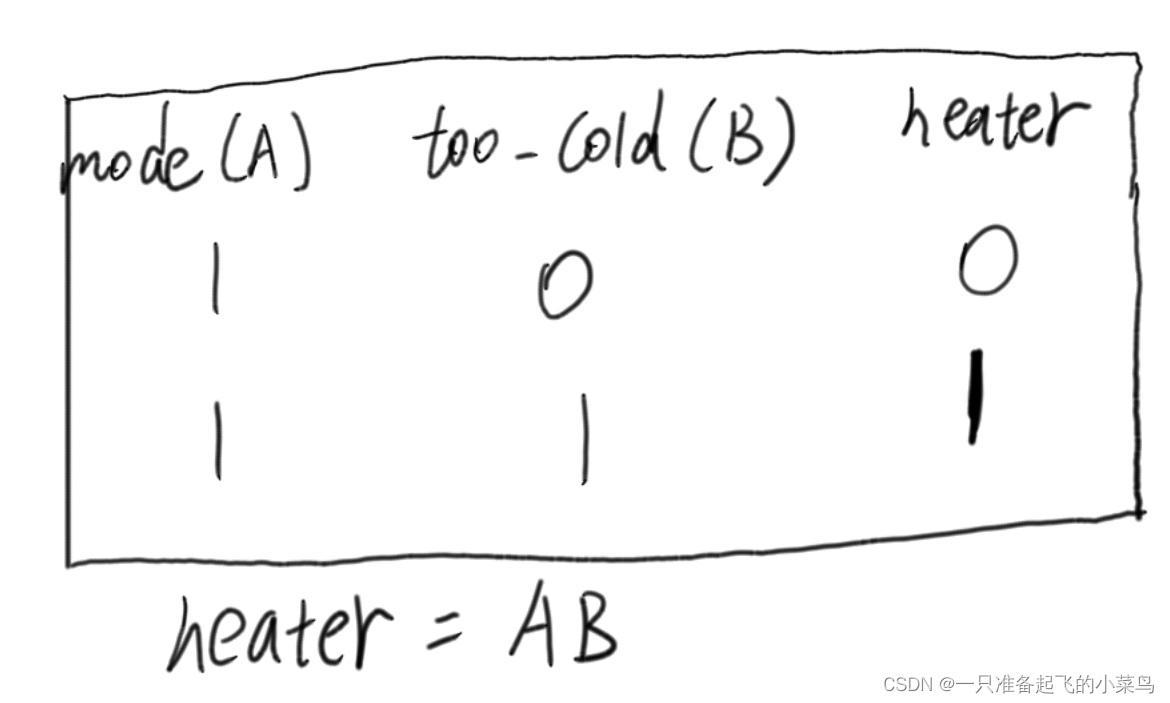

由题可知,加热器(heater)是否打开主要与模式(mode)和过冷信号(too_cold)有关,所以对其列真值表得到,加热器(heater)的开关值逻辑表达式。

由题可知,加热器(heater)是否打开主要与模式(mode)和过冷信号(too_cold)有关,所以对其列真值表得到,加热器(heater)的开关值逻辑表达式。

同理可以得出,风扇开关(fan)与fan_on(代号d)和heater、aircon有关。所以得出其逻辑表达式为:fan=(!AC)+AB+d,即相当于加热棒加热打开风扇、空调打开同时也打开风扇、同时风扇由fan_on控制。

1.4 原理和代码讲解

module top_module (

input too_cold,

input too_hot,

input mode,

input fan_on,

output heater,

output aircon,

output fan

);

assign fan=(!mode&too_hot)|(mode&too_cold)|fan_on;

assign heater=mode&too_cold;

assign aircon=!mode&too_hot;

endmodule